-

- ARIS-RP1: Design and Characterization of Ultra-Large-Scale Intelligent Electromagnetic Surfaces Using Deep Learning

- ARIS-RP2: Reprogrammable Meta-optics for Information Multiplexing

- ARIS-RP3: Making Wireless Communication Environment Smart via Reconfigurable Intelligent Surfaces (RIS): A New Network Optimization Perspective

-

- FCT-RP1: Practical Data Storage and Computation in DNA Molecules

- FCT-RP2: Amorphous-Oxide-Semiconductor Thin Film Transistors and DRAM Cross-bar to Enable 3D Monolithically Integrated Architecture for Near/In-memory Computing

- FCT-RP3: Neural-like Computing System based on Superparamagnetic Tunnel Junctions

-

- HFM-RP1: Wearable Microneedle Patch for the Minimally Invasive Wireless Continuous Glucose Monitoring

- HFM-RP2: On-body computing for Next-generation Wearable Systems

- HFM-RP3: A Novel Optical Biometer to Monitor Myopia Progression in Children.

- HFM-RP4: Magnetoplethysmograph for Continuous Heart Rate and Blood Pressure Monitoring

- HFM-RP5: Manufacturing of Artificial SKin Integrated Network (SKIN) for Healthcare and Fitness Monitoring

- HFM-RP6: Radio-frequency Textile Sensors for Wearable and Ambient Health Monitoring

-

- ADT-RP1: Development of High Precision Additive Manufacturing for Integrated Complex Molding Applications

- ADT-RP2: Low Loss and Tunable Ferroelectrics for Sub-6G Applications

- ADT-RP3: Redox-mediated Flow Battery for Household Energy Storage

- ADT-RP4: Development of Nature-inspired Multiscale Composite Materials for High Strength and Low Loss Applications

-

- WDSS-RP1: Enabling Continuous and Realtime Monitoring of Human Vitals through Battery-free Tunnel Diode based Sensors

- WDSS-RP2: Wireless Communication and Radar Sensing Fusion Based Indoor Localization

- WDSS-RP3: Multi-parameter Sensing Platform for Proactive Hypertension Diagnostics Using Artificial Intelligence

- WDSS-RP4: LightChips: Light-Based Integrated Cloud-to-Edge Communications, Sensor Node Wake-Up and Indoor Positioning for mm-Scale Purely-Harvested Systems

FCT-RP2: Amorphous-Oxide-Semiconductor Thin Film Transistors and DRAM Cross-bar to Enable 3D Monolithically Integrated Architecture for Near/In-memory Computing

Principal Investigator: Assistant Professor Gong Xiao, ECE

Co-Principal Investigator: Professor Aaron Thean, CDE

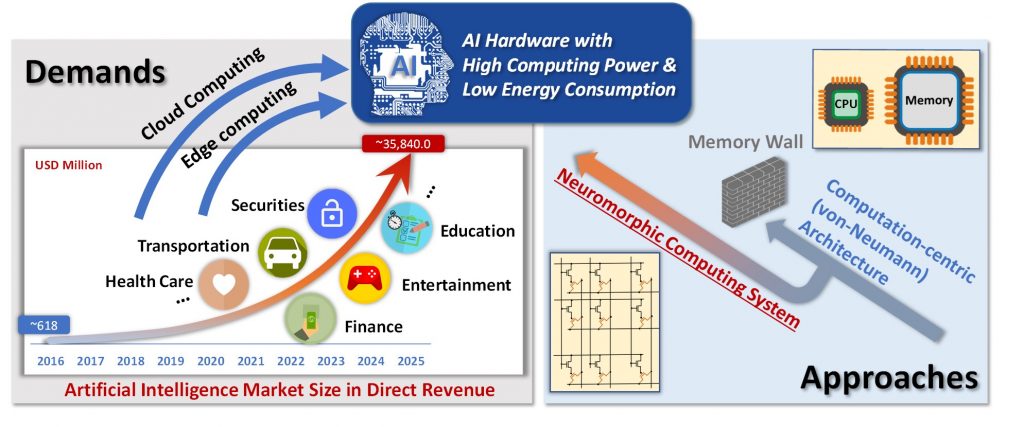

The data intensive and data centric computing calls for a paradigm shift of computing hardware platform to address tremendous but important challenges facing future computing that cannot be merely answered by commonly pursued approaches such as continuous down-scaling and performance improvement in Si-based transistors, distributed and parallel computing based on von- Neumann architecture, and 2D/2.5 system integration approach. There is an urgent need to search for innovative ways to tackle ‘the memory wall’ where a large amount of data needs to be fetched and stored during the computation which is both time and energy consuming.

Two effective solutions would be (1) co-locating computation blocks and memories for highband width data traffic; and (2) empowering memories with computational capability such as neuromorphic computing where chips are directly inspired by biological neural circuits so that they can process new knowledge, adapt, and learn in real time at unprecedented low power levels. A neuromorphic architecture stores the data (weights) in the non-volatile memory devices (analog synapses) and uses crossbar structures to realize large-scale matrix operations, which is similar to the behaviour of the synapses and neuron in the human brain. Essentials to the neuromorphic architecture include the analog synapse device with multiple states, low latency, high endurance, and high retention, as well as the integration of these high density synapse devices with peripheral circuits in a 3D manner.

In this proposal, we aim to work on amorphous-oxide semiconductor (AOS) thin film transistors (TFTs) and dynamic random access memory (DRAM) having back-end-of-line (BEOL) compatible processes, extremely low power, good scalability, and low cost, to enable efficient near and inmemory computing in a 3D monolithic integration manner that promises to deliver significant improvement in latency, energy, and cost as compared with the state-of-the-art nano-electronic systems, as shown in the figure below. Our proposed work would cut across the disciplines of materials, devices, circuits, and systems and is highly relevant to many major industry players and promises to spearhead the transformation of nano-electronic hardware platform for future computing.