Using Cadence NCLaunch and Silicon Ensemble, Synopsys Chip Synthesis and PrimeTime

Version 1.0

By

Zheng Huan Qun March 2006

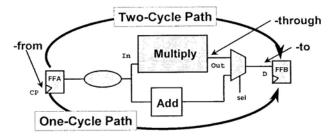

Department of Electrical and Computer Engineering National University of Singapore

| AUTH  | OR'S NOTE                                                                     |        |

|-------|-------------------------------------------------------------------------------|--------|

| 1. II | TRODUCTION                                                                    | 5      |

| 1.1   | Prerequisite                                                                  | 5      |

| 1.2   | OVERVIEW OF ASIC DESIGN                                                       |        |

| 1.3   | ARRANGEMENT OF THE MANUAL                                                     |        |

| 1.3   | ENVIRONMENT SETUP.                                                            |        |

|       | DDING FOR SYNTHESIS                                                           |        |

|       |                                                                               |        |

| 2.1   | IF STATEMENTS                                                                 |        |

| 2.2   | CASE STATEMENTS                                                               |        |

| 2.3   | LOOP STATEMENTS                                                               |        |

| 2.4   | PARTITIONING A DESIGN                                                         |        |

| 2.5   | CONCLUSION                                                                    |        |

| 3. R  | TL SIMULATION AND VERIFICATION WITH CADENCE NCLAUNCH                          |        |

| 3.1   | INTRODUCTION TO NCLAUNCH                                                      | 13     |

|       | 1.1 Invoking NCLaunch                                                         |        |

|       | 1.2 Single-Step and Multi-Step Modes                                          |        |

|       | 1.3 Components of NCLaunch                                                    |        |

|       |                                                                               |        |

|       |                                                                               |        |

| 3.2   |                                                                               |        |

|       |                                                                               |        |

|       |                                                                               |        |

| 3.    | D.2 Compiling and Elaborating the Design         3.2.2.1 Compiling the Design |        |

|       | 3.2.2.2 Elaborating the Design                                                |        |

| 3     | 2.3 Starting the Simulator                                                    |        |

|       | 2.4 Simulating the Design                                                     |        |

| 5.    | 3.2.4.1 Selecting the Simulation Data to Save                                 |        |

|       | 3.2.4.1 Selecting the Simulation Data to Save                                 |        |

| 3     | 2.5 Displaying Simulation Data                                                |        |

|       | 3.2.5.1 Selecting the Signals to Display                                      |        |

|       | 3.2.5.2 Moving through Simulation Time                                        |        |

|       | 3.2.5.3 Moving the Cursors                                                    |        |

| 3.3   | 5                                                                             |        |

| 3.    | 8.1 Searching for Conditions                                                  |        |

| 3.    | 8.2 Analyzing Simulation Data in the Waveform Window                          |        |

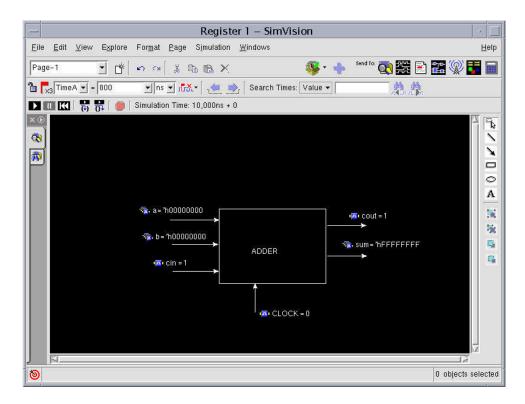

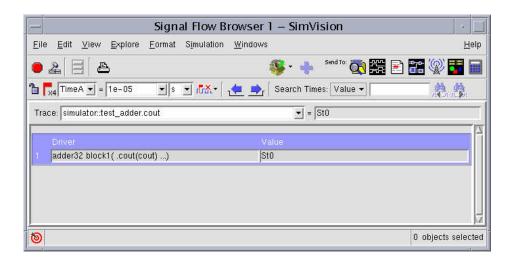

|       | 8.3 Analyzing Simulation Data in the Register Window                          |        |

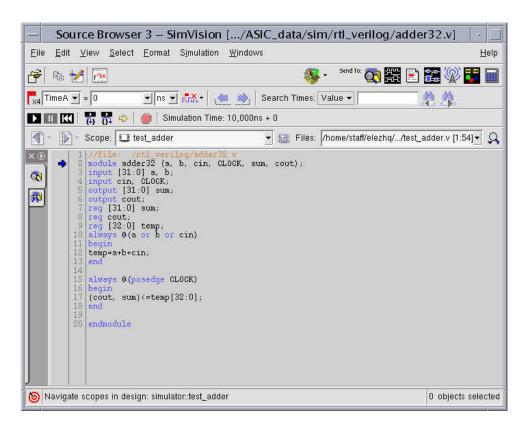

|       | 8.4 Fixing an Error in the Source Code                                        |        |

|       | 8.5 Ending a SimVision Session                                                |        |

| 3.4   | Conclusion                                                                    |        |

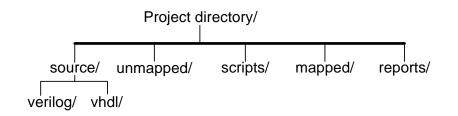

| 4. L  | OGIC SYNTHESIS AND OPTIMIZATION USING SYNOPSYS CHIP SYN                       | THESIS |

|       | N COMPILER)                                                                   |        |

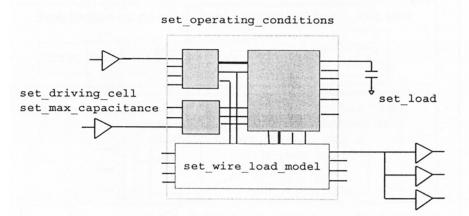

| 4.1   | INTRODUCTION TO SYNTHESIS AND OPTIMIZATION                                    |        |

| 4.2   | PREPARATIONS FOR USING DESIGN COMPILER                                        |        |

| 4.    | 2.1 Prescriptions of the .synopsys_dc.setup File                              |        |

| 4.    | 2.2 Prescriptions of Constraint File                                          |        |

|       | 4.2.2.1 Timing Goals                                                          |        |

|       | 4.2.2.2 Environmental Attributes                                              |        |

|       | 4.2.2.3 Design Rules and Area Constraints - Optional                          |        |

|       | 2.3 Synthesizing and Optimizing a Design                                      |        |

| 4.    | 2.4 Generating and Checking Reports                                           |        |

|       | 4.2.4.1 Report Constraints                                                    |        |

|       | 4.2.4.2 Report Timing                                                         |        |

|    | 4.3            | METHODS TO FIX VIOLATIONS                                          | 44  |

|----|----------------|--------------------------------------------------------------------|-----|

|    | 4.3.1          | Fix Design Rule Violation                                          | 44  |

|    | 4.3.2          | Fix Timing Violations                                              |     |

|    | 4.3.3          | Other Options                                                      |     |

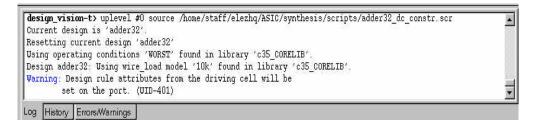

|    | 4.4            | TUTORIAL OF USING DESIGN COMPILER                                  | 45  |

|    | 4.4.1          | Preparations                                                       |     |

|    | 4.4.2          | Synthesizing and Optimizing a Design                               |     |

|    | 4.4            | 1.2.1 Read and Link Design                                         |     |

|    | 4.4            | I.2.2 Constraining Design                                          |     |

|    | 4.4            | 1.2.3 Compiling a Design                                           |     |

|    | 4.4            | 1.2.4 Generating Reports                                           |     |

|    | 4.4.3          | Insert Pads                                                        | 55  |

|    | 4.5            | CONCLUSION                                                         | 56  |

| 5. | DDF            | -LAYOUT VERIFICATION WITH NCLAUNCH                                 | 57  |

| 5. | PKL            | LAYOUT VERIFICATION WITH NCLAUNCH                                  |     |

|    | 5.1            | OVERVIEW OF SDF ANNOTATION                                         |     |

|    | 5.2            | \$SDF ANNOTATE SYSTEM TASK                                         |     |

|    | 5.3            | <b>REQUIREMENTS FOR </b> <i>\$SDF</i> <b>ANNOTATE SYSTEM TASKS</b> | 59  |

|    | 5.4            | TUTORIAL OF PRE-LAYOUT VERIFICATION USING NCLAUNCH                 |     |

|    | 5.4.1          |                                                                    |     |

|    | 5.4.2          |                                                                    |     |

|    | 5.4.3          | Elaborating Design                                                 |     |

|    | 5.5            | Conclusion                                                         |     |

|    |                |                                                                    |     |

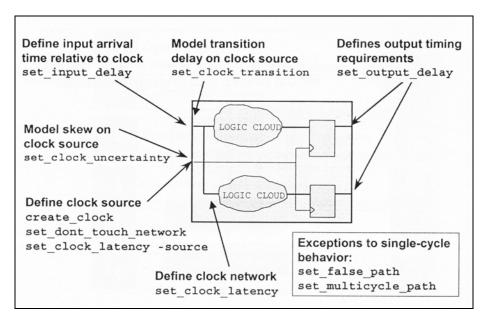

| 6. | PRF            | C-LAYOUT TIMING ANALYSIS USING SYNOPSYS PRIMETIME                  | 67  |

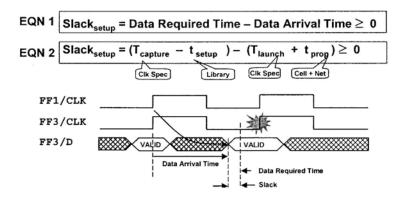

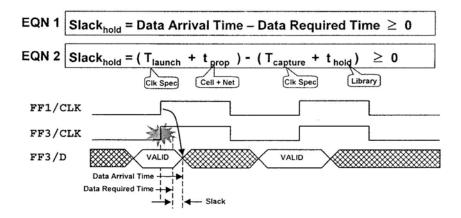

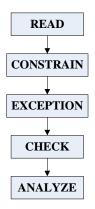

|    | 6.1            | INTRODUCTION TO STATIC TIMING ANALYSIS                             | 67  |

|    |                | READING DESIGN DATA                                                |     |

|    |                |                                                                    |     |

|    | 6.3            | CONSTRAINING DESIGN                                                |     |

|    | 6.4            | SPECIFYING TIMING EXCEPTIONS                                       |     |

|    | 6.5            | CHECKING AND ANALYZING                                             |     |

|    | 6.5.1          | - · · · ð                                                          |     |

|    | 6.5.2          |                                                                    |     |

|    | 6.6            | TYPES OF STATIC TIMING ANALYSIS                                    |     |

|    | 6.7            | TUTORIAL OF USING PIMETIME                                         | 73  |

|    | 6.7.1          | Preparations                                                       |     |

|    | 6.7.2          | Invoking PrimeTime GUI and Verify Setup                            |     |

|    | 6.7.3          | Reading, Constraining and Checking Design                          |     |

|    | 6.7.4          | Analyzing Design                                                   |     |

|    | 6.7.5          | Generating Reports                                                 | 80  |

|    | 6.7.6          | Exit PrimeTime                                                     |     |

|    | 6.8            | Conclusion                                                         |     |

|    |                |                                                                    |     |

| 7. | PLA            | ACE AND ROUTE WITH CADENCE SILICON ENSEMBLE                        |     |

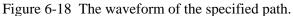

|    | 7.1            | OVERVIEW OF SILICON ENSEMBLE FLOW                                  | 87  |

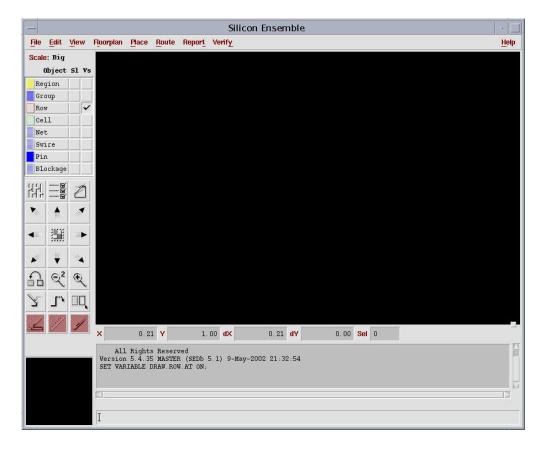

|    |                | SE GRAPHICAL INTERFACE AND ONLINE HELP                             |     |

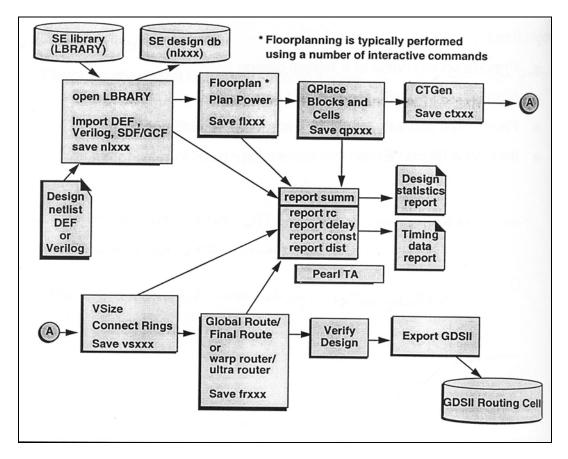

|    | 7.2.1          | SE Graphical Interface                                             |     |

|    | 7.2.1          |                                                                    |     |

|    |                |                                                                    |     |

|    |                | INTRODUCTION TO THE STARTING SCRIPTS OF AMS KITS                   |     |

|    | 7.4            | TUTORIAL OF USING SILICON ENSEMBLE WITH AMS KITS                   |     |

|    | 7.4.1          | Setup for Using SE and AMS Kits                                    |     |

|    | 7.4.2          | Loading LIBRARY                                                    |     |

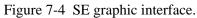

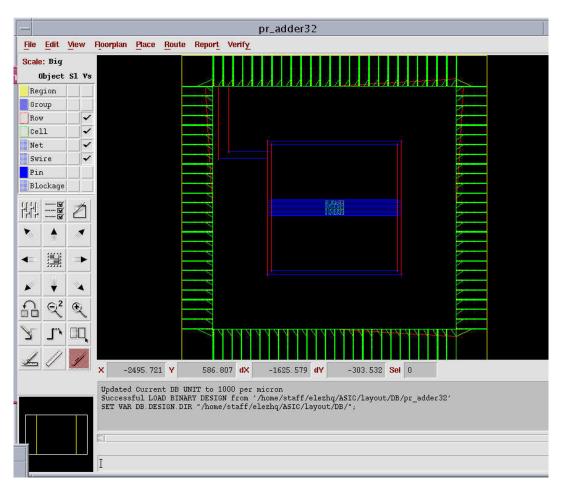

|    | 7.4.3          | Importing Design and Initializing Floorplan                        |     |

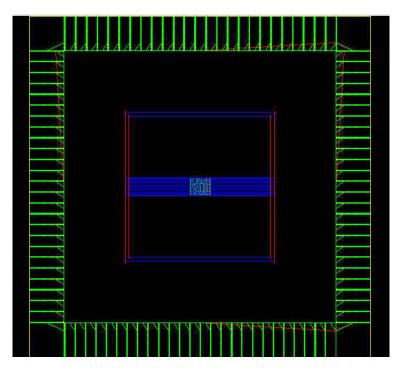

|    | 7.4.4          | Viewing the Floorplan                                              |     |

|    | 7.4.5          | Power Planning                                                     |     |

|    | 7.4.6          | Place Cells                                                        |     |

|    | 7.4.7          | Clock Tree Generation                                              |     |

|    | 7. <b>4</b> .8 | Place Filler Cells                                                 |     |

|    | 7.4.9          | Viewing a Placed Database                                          | 103 |

|    |                | -                                                                  |     |

| 7.      | 4.9.1 Viewing Placed Cells                  |  |

|---------|---------------------------------------------|--|

| 7.      | 4.9.2 Viewing Pins                          |  |

| 7.      | 4.9.3 Viewing Nets                          |  |

| 7.4.1   | 0 Routing Power Nets                        |  |

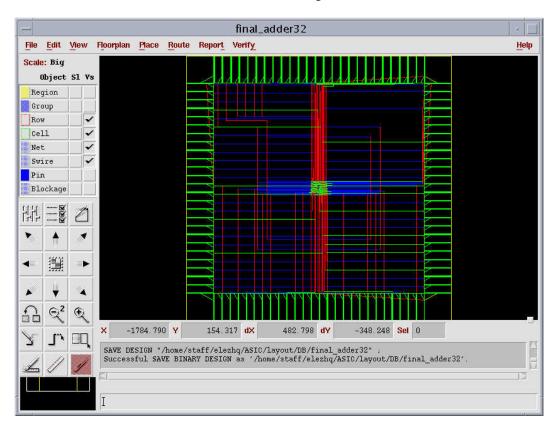

| 7.4.1   | 1 Routing all the Nets                      |  |

| 7.4.1   | 2 Viewing the Routed Design                 |  |

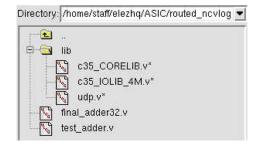

| 7.4.1   | 3 Exporting Design                          |  |

| 7.5     | Conclusion                                  |  |

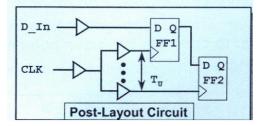

| 8. POS  | T-LAYOUT VERIFICATION WITH NCLAUNCH         |  |

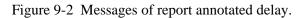

| 9. POS  | T-LAYOUT STA WITH PRIMETIME                 |  |

| 9.1     | OVERVIEW OF POST-LAYOUT STA                 |  |

| 9.1.1   | Parasitic versus SDF                        |  |

| 9.1.2   | Back-Annotation Command Summary             |  |

| 9.1.3   |                                             |  |

| 9.2     | CONSTRAINTS OF POST-LAYOUT STA              |  |

| 9.3     | TUTORIAL OF POST-LAYOUT STA USING PRIMETIME |  |

| 9.3.1   | Preparations                                |  |

| 9.3.2   |                                             |  |

| 9.4     | CONCLUSION                                  |  |

| REFEREN | NCE                                         |  |

# **Author's Note**

Writing this manual has provided me with a valuable opportunity to study ASIC design, which bears significant difference from the analog design that I was accustomed to doing. During this enriching process, I gained understanding of ASIC design and learn all the EDA tools required for it. All of this commenced with a search for books on ASIC design to mastering EDA tools and finally finishing the manual after a year's effort. I strived to make the contents, to the largest extent possible, parallel to practical work. May this manual become the handy guide for our students and staff who will be doing ASIC design. I hope that you may kindly provide me with useful feedback. Please email me at <u>elezhq@nus.edu.sg</u>.

Zheng Huan Qun 16 March 2006

# **1. Introduction**

This manual describes the method of ASIC design from front-end to back-end using cadence NCLaunch, cadence silicon ensemble, synopsys chip synthesis and primetime.

The manual is meant for the beginners of ASIC design. The usages of the cadence and synopsys tools are demonstrated with graphic user interface (GUI), for users understand easily and apply conveniently.

# **1.1 Prerequisite**

Users need to know Hardware Description Language (HDL), either VHDL or Verilog, and are able to write RTL code with HDL. Users must have the knowledge of digital circuits.

# **1.2 Overview of ASIC Design**

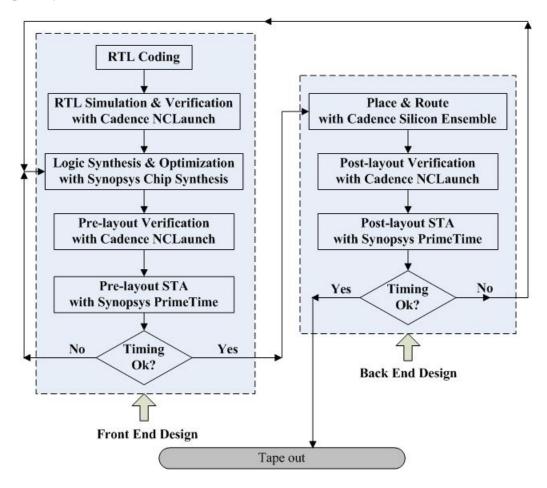

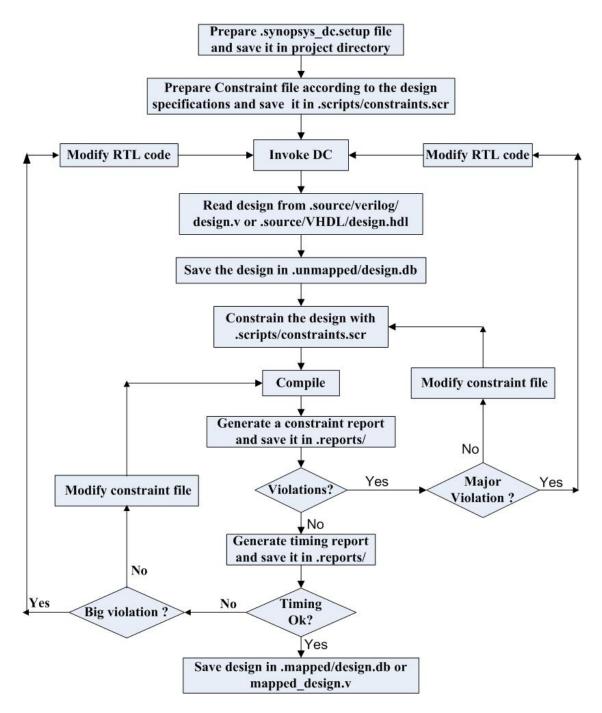

ASIC design flow is shown in figure 1-1. As it shows, the front-end design includes RTL coding, RTL functionality verification, synthesis, pre-layout verification and pre-layout static time analysis (STA), and the back-end design includes place and route, post-layout verification and post-layout STA.

Figure 1-1 ASIC design flow.

The explanation of the flow is as follows.

- RTL coding to code design with HDL.

- RTL Simulation & Verification to simulate the RTL code and verify that the code is logically and functionally right.

- Logic Synthesis & Optimization to synthesis and optimize the code and get the gate level netlist of the design.

- Pre-layout Verification to verify that the gate level netlist satisfies the specifications of the design.

- Pre-layout STA to do static timing analysis with standard cell delays and wire load models.

- Place & Route to get the layout of the design.

- Post-layout Verification to verify the layout level netlist satisfies the specifications of the design.

- Post-layout STA to do static timing analysis with standard cell delays, net delays and parasitics.

The design can be taped out if the design satisfies its specifications after post-layout STA. If not, it has to be brought back to synthesize and optimize again. If no matter how hard the synthesis level it takes and the design still cannot meet the specifications, modifying the source (RTL) code has to be considered.

# **1.3** Arrangement of the Manual

RTL coding style affects the final chip synthesis results directly, so understanding the hardware implications for coding constructs is important. The hardware implications for code - *if-else, case* and *for loop* are described briefly in *chapter 2*. Advanced users may refer to synopsys documents or HDL books for more information.

In *chapter 3*, the usage of cadence NCLaunch is described and demonstrated. The steps to compile, elaborate and simulate a Verilog (or VHDL) design are listed in details, and the steps to save & view output data are listed in details too. The verification of RTL code using NCLaunch is demonstrated with a 32 bit adder. The method described in this chapter will be used during prelayout and post-layout verification.

Once it is verified that the RTL code is logically and functionally right. The code is brought to synopsys chip synthesis for synthesizing and optimizing to get a gate level netlist. The method of synthesis and optimization is described, and the normal steps of running chip synthesis are listed in *chapter 4*. The whole flow is demonstrated with the 32 bit adder RTL code which has passed the verification in chapter 3.

Does the gate level netlist meet the specifications of the design? A pre-layout verification needs to be done using NCLaunch. The difference between pre-layout and RTL code verification is that the standard cell delays are considered while simulating the pre-layout netlist (the gate level netlist). The delay information is saved in a standard delay format (SDF) file which is got from chip synthesis. *Chapter 5* focuses on SDF back annotation system task. The demonstration is done with the 32 bit gate level netlist which is the output of chapter 4.

In *chapter 6*, the pre-layout STA using primetime is described. Pre-layout STA is to check the timing of the design. The method of doing STA using primetime is demonstrated with the 32 bit adder gate level netlist in this chapter.

After the design is verified, its gate level netlist can be brought to cadence silicon ensemble for place and route to get its layout. The full steps from setting up library, floor planning, cell placement, power ring creation and clock generation to route are demonstrated with the design example -32 bit adder in *chapter 7*.

Post-layout verification is presented and demonstrated in *chapter 8*. Like pre-layout verification, SDF back annotation is used to annotate the design. The difference between post-layout and pre-layout verification is that the post-layout SDF file includes both delays of standard cells and nets while pre-layout SDF file has the standard cell delays only.

Post-layout STA using primetime is described in *chapter 9*. A SDF file including delay information of the design and a reduced standard parasitic format (RSPF) file including the parasitics are used to back annotate the design during STA. The method to back annotate the design is demonstrated with the 32 bit adder in this chapter.

## **1.4 Environment setup**

To use the ASIC design manual, the following tools are needed,

- Cadence NCLaunch,

- Cadence Silicon Ensemble,

- Synopsis Chip Synthesis, and

- Synopsys PrimeTime.

The environment setup for using the above tools has to be done. Ask your system administrator for help.

# 2. Coding for Synthesis

Code that is functionally equivalent, but coded differently, will give different synthesis results. User cannot rely solely on Design Complier (DC) to fix a poorly coded design. Try to understand the "hardware" coded, to give DC the best possible starting point. The three big guidelines to write RTL code are as follows.

- Write HDL hardware descriptions and think of the topology implied by the code.

- Do not write HDL simulation models without explicit delays and file I/O.

- Isolate asynchronous logic from synchronous logic as synchronous designs run smoothly through synthesis test, simulation, and layout.

Keep in mind that writing in an RTL coding style means describing the register architecture, circuit topology and functionality between registers, and that DC optimizes logic between registers only not the register placement.

This chapter describes briefly hardware implication for some statements: *if*, *case* and *loop*. Partitioning a design is presented in this chapter, too.

# 2.1 *if* statements

➢ if-else statements

| Code 1:           | Code 2:        |

|-------------------|----------------|

| if (SEL=`1`) then | if (SEL==1`b1) |

| SUM<=A+B;         | begin          |

| else              | OP1=A;         |

| SUN<=C+D;         | OP2=B;         |

| End if;           | end            |

|                   | else           |

|                   | begin          |

|                   | Op1=C;         |

|                   | Op2=D:         |

|                   | end            |

|                   | SUM=Op1+Op2;   |

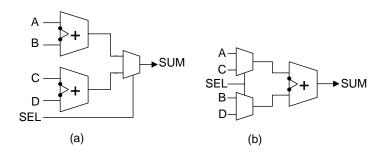

Code 1 construct implies multiplexing hardware figure 2-1 (a) or figure 2-1 (b). Code 2 implies figure 2-1 (b) only. Both codes are functionally same.

Figure 2-1 Implication of if-else.

#### ➢ if statements and Latches

Any signal that is not fully specified for all conditions infers a latch. Below is the code example of VHDL/Verilog.

| VHDL code 1:                | Verilog code 2:         |

|-----------------------------|-------------------------|

| LS373: process (ALE, ADBUS) | Always @ (ALE or ADBUS) |

| begin                       | begin                   |

| If $(ALE=1)$ then           | If (ALE)                |

| ABUS<=ADBUS;                | ABUS=ADBUS;             |

| end if;                     | end                     |

| end process LS373           |                         |

## if-then-elseif statements

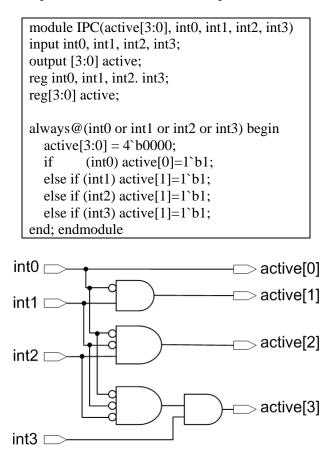

VHDL and Verilog *if-elseif* statements imply priority, use only if priority checking is a circuit requirement. Priority control logic will be synthesized, resulting in a larger and possibly slower logic, if it is used. An example is shown below, and its implication is shown in figure 2-2.

Figure 2-2 Implication of if-then-elseif.

There are cases where there is no need to use *if-then-elseif*, and they are

- when input signals have equal priority (no priority over each other), and

- when signals are mutually exclusive.

# 2.2 Case Statements

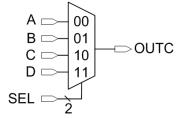

Case statements imply parallel MUX function, as shown in figure 2-3. The actual gates synthesized might not be a 4:1 MUX, and they depend on the target library used.

| VHDL code:                      | Verilog code:                    |

|---------------------------------|----------------------------------|

| VIIDL COUE.                     | vennog coue.                     |

| process (SEL, A, B, C, D) begin | always@(SEL or A or B or C or D) |

| case SEL is                     | begin                            |

| when "00"=>OUTC <= A;           | case (SEL)                       |

| when " $01$ "=>OUTC <= B;       | $2^{b00}: OUTC = A;$             |

| when "10"=>OUTC $\leq$ C;       | $2^{b01} : OUTC = B;$            |

| when others=> OUTC <= D;        | $2^{b10}: OUTC = C;$             |

| end case;                       | default : $OUTC = D;$            |

| end process;                    | endcase                          |

| _                               | end                              |

Figure 2-3 Implication of case statements.

# 2.3 Loop statements

#### Unrolling loops

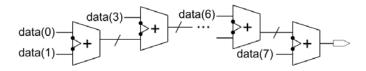

In synthesis, *for* loops are "unrolled" during translation, and then synthesized. For the code below, its hardware is shown in figure 2-4.

| Verilog code:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| integer i;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| always@(a or b ) begin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| for $(i = 0; i \le 3; i=i+1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Out[i] = a[i] & b[3-i];                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| $ \begin{array}{c} a(0) \\ b(3) \\ a(1) \\ b(2) \\ a(2) \\ b(1) \\ a(2) \\ b(1) \\ a(2) \\ b(1) \\ a(2) \\ b(2) \\ a(2) \\ b(1) \\ a(2) \\ b(2) \\ a(2) \\ b(1) \\ a(2) \\ a(2) \\ b(1) \\ a(2) \\ a(2) \\ b(1) \\ a(2) \\ a(2) \\ b(2) \\ a(2) \\ a(3) \\ a$ |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

a(3) \_\_\_\_\_ out(3)

Figure 2-4 Implication of unrolled loop.

> **Tradeoffs** with loops

| VHDL code:               | Verilog code:                     |

|--------------------------|-----------------------------------|

| process (data)           | always@(data)                     |

| variable sum; integer;   | begin                             |

| h a shu                  |                                   |

| begain                   | sum = 0;                          |

| sum := 0;                | /*count the numer of '1's*/       |

| count the 1's            | for $(i = 0; i < 8; i = i+1)$     |

| for i in 0 to 7 loop     | sum = sum + data[i];              |

| sum := data(i) + sum;    |                                   |

| end loop                 | /* check if even or odd number */ |

| -                        | $odd_parity = sum[0]$             |

| check parity             |                                   |

| odd_parity <= sum mod 2; | end                               |

| end process              |                                   |

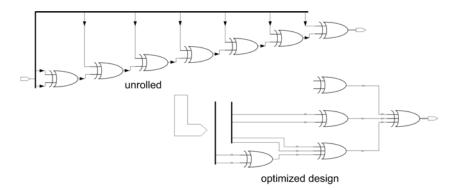

The hardware for the above code is shown in figure 2-5.

Figure 2-5 Implication of tradeoffs with loop.

# Recoded loop

| VHDL code:                            | Verilog code:                 |

|---------------------------------------|-------------------------------|

| process (data)                        | always@(data)                 |

| variable odd-parity : bit;            | begin                         |

| begin                                 | for $(i = 0; i \le 8; i=i+1)$ |

| odd_parity <= '0';                    | odd_parituy = ^data[i];       |

| for i in 0 to 7 loop                  | end                           |

| odd_parity <= data(i) xor odd_parity; |                               |

| end loop;                             |                               |

| end process                           |                               |

The hardware implication of the above code is shown in figure 2-6.

Figure 2-6 Implication of recoded loop

# 2.4 Partitioning a Design

Partitioning is the process of dividing complex design into smaller parts. Ideally, all partitions would be planned prior to writing any RTL. Initial partitions of a design are defined by RTL, but it can be modified using DC by the commands: *group* and *ungroup*<sup>1</sup>. The followings determine the partitions within the RTL description.

- *Entity* and *module* statements define hierarchical blocks,

- Inference of arithmetic circuits (+, -, \*, ..) can create a new level of hierarchy, and *Process* and *Always* statements do not create hierarchy.

The partitioning strategies for synthesis are shown below.

- Don't separate combinational logic across hierarchical boundaries.

- Place hierarchy boundaries at register outputs.

- Size blocks for reasonable runtimes.

- Separate core logic, pads, clocks, asynchronous logic and JTAG.

A design with better partitioning brings

- better results: smaller and faster design,

- easier synthesis process: simplified constraints and scripts, and

- faster compiles: quicker turnaround.

Remember: always plan the partitioning of design prior to start writing RTL code.

# 2.5 Conclusion

This chapter lists the hardware implications for some statements, and highlights the importance of partitioning a design. Reader should keep these in mind and remember that DC optimizes logic between registers only not the register placement.

<sup>&</sup>lt;sup>1</sup> Refer to Synopsys Design Compiler document for details.

# 3. RTL Simulation and Verification with Cadence NCLaunch

Once coded, simulation and verification should be done to verify the code and its functionality. This can be achieved with either cadence tool (NCLaunch) or synopsys tool (VCS). In this manual, NCLaunch is introduced and used.

The arrangement is as follows. In section 3.1, an introduction to NCLaunch software is presented. In section 3.2, a tutorial of using NCLaunch is preformed. The method of debugging a design is given in section 3.3. The conclusion is given in section 3.4. The whole process is demonstrated with a 32 bit adder which is coded with Verilog.

# **3.1 Introduction to NCLaunch**

NCLaunch provides user with a graphical user interface to configure and launch cadence simulation tools: compiler, elaborator and simulator. The following concepts are described in this section, which user should be familiar before running NCLaunch.

- Invoking NCLaunch

- Single-Step and Multi-Step Modes

- Components of NCLaunch

- Exiting NCLaunch

- The NCLaunch Help Menu

#### 3.1.1 Invoking NCLaunch

On UNIX system, invoke NCLaunch with the following commands.

% nclaunch – new<sup>2</sup> (first time)

#### % nclaunch (afterwards)

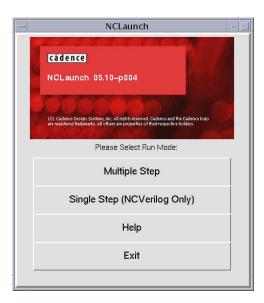

When NCLaunch starts for the first time, it prompts user to select a running mode, *single-step* and *multi-step*, as shown in figure 3-1.

Figure 3-1 Select running mode.

<sup>&</sup>lt;sup>2</sup> There are more options. Please refer to NCLunch User Guide for details

## 3.1.2 Single-Step and Multi-Step Modes

NCLaunch allows user to invoke the simulator in one of the following two modes:

- In multi-step mode<sup>3</sup>, user performs separate steps to compile source files, elaborate design units, and simulate snapshots for Verilog, VHDL, and mixed-language designs. This gives user greatest control and flexibility to specify simulation options and features. Multiple step mode uses the *ncvlog* and *ncelab* commands to compile and elaborate design.

- In single-step mode<sup>4</sup>, user compiles, elaborates, and simulates a design in one step. For designs entirely written in Verilog, this provides an easy way to select NC-Verilog options and run the simulation. Single-step mode creates everything needed to run the NC-Verilog simulator, including all directories, a cds.lib file, and an hdl.var file. Single step mode uses the *ncverilog* command to compile and elaborate design.

User can switch mode at any time by selecting  $File \rightarrow Switch$  to Multiple Step or File  $\rightarrow Switch$  to Single Step.

#### 3.1.3 Components of NCLaunch

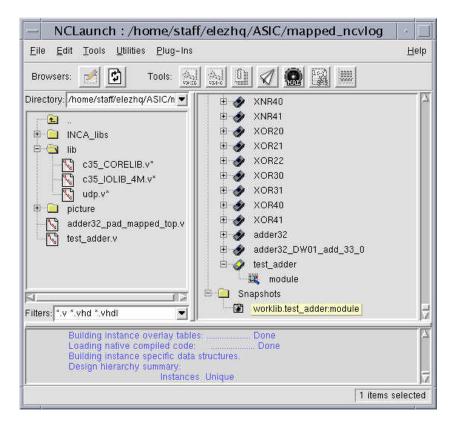

The NCLaunch main window contains a menu bar, toolbar, file browser or design area, and an I/O region. Figures 3-2 and 3-3 show the main window in multi-step mode and single-step mode respectively.

- Menu Bar contains the *File*, *Edit*, *Tools*, *Utilities*, *Plug-ins*, and *Help* menu choices.

- **ToolBar** consists of icons that invoke cadence NC simulation tools and utilities. The tool icons give user a shortcut to the tools, as shown in Table 3-1.

- **I/O Region and Status Bar** let user submit batch commands to simulation tools and utilities and view the output of running process. Standard output messages from running processes are displayed in blue and error messages are displayed in red.

| - NCLaunch : /home/staff/ele                                       | zhq/ASIC/ASIC_data/sim |

|--------------------------------------------------------------------|------------------------|

| <u>File E</u> dit <u>T</u> ools <u>U</u> tilities <u>P</u> lug-Ins | Help                   |

| Browsers: 🛃 🚺 Tools: 🔬                                             |                        |

| Directory: nome/staff/elezhq/ASIC/ASIC_(<br>inclaunch>             |                        |

|                                                                    | 0 items selected       |

Figure 3-2 NCLaunch main window, multi-step mode.

<sup>&</sup>lt;sup>3,4</sup> For more information, refer to the NC-Verilog Simulator Help.

| - NCLaunch : /home/staff/elezhq/ASIC/ASIC_dat                                                               | a/sim 🕢 🗌        |

|-------------------------------------------------------------------------------------------------------------|------------------|

| <u>F</u> ile <u>E</u> dit <u>T</u> ools <u>U</u> tilities <u>P</u> lug-Ins <u>B</u> uttons                  | <u>H</u> elp     |

| Browsers: 🛃 💽 Tools: 🏹 🎆 🛄                                                                                  |                  |

| Directory: nome/staff/elezhq/ASIC/ASIC_   Design  Design  INCA_libs  Tl_verilog  waves.shm adder32.v  top.v | *                |

| Filters: ".v                                                                                                |                  |

| <u> </u>                                                                                                    | 0 items selected |

Figure 3-3 NCLaunch main window, single-step mode.

Table 3-1 Icons of the toolbar.

| Icons        | Function                                                                                                                                                |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Edit File – by selecting a file and clicking on this icon, a text editor appears with the file's contents for review or modification.                   |

| t,           | Refresh – Updates user's browser window.                                                                                                                |

| A CALL       | Compile VHDL Files (multi-step only) – compiles selected VHDL files that appear as design units under user's work library in the Library Browser.       |

| 1012<br>1012 | Compile Verilog Files (multi-step only) – compiles selected Verilog files that appear as design units under user's work library in the Library Browser. |

|              | Elaborate Files (multi-step only) – by selecting the top level design unit and clicking on this icon, user's design is elaborated.                      |

| L.           | Run Simulation – starts a simulation of selected design.                                                                                                |

| Real         | Launch analysis & lint with current selection                                                                                                           |

|              | Browser Logfiles – launches the NCBrowse message browser to analyze selected log files.                                                                 |

| 0000         | Waveform Viewer – starts the SimVision analysis environment with selected database files.                                                               |

| nclaunch> |  |

|-----------|--|

|           |  |

|           |  |

|           |  |

|           |  |

|           |  |

#### 3.1.4 Exiting NCLaunch

To exit NCLaunch, select **File→Exit**.

Exiting the application does not terminate any batch jobs that user has already launched. On exit, NCLaunch saves general default settings to user's home directory, and saves design default setting to user's current working directory.

#### 3.1.5 Environment Setup

User can run NCLaunch in one of the two modes, single step or multiple step. As mentioned in section 3.1.2, single step mode provides all the necessary setup files (cds.lib and hdl.var), while multiple step mode creates those setup files through a few steps of setting. A sample of setting environment is shown in section 3.2.1.

# 3.2 Tutorial of Using NCLaunch

The sample used here is a 32 bit adder, and its source code adder32.v and  $test_adder.v$  are listed in tables 3-2 and 3-3 respectively. The file  $test_adder.v$  which tests the function of the adder32.v is the top design.

| <br>//file: ~/project/rtl_verilog/adder32.v   |

|-----------------------------------------------|

| module adder32 (a, b, cin, CLOCK, sum, cout); |

| input [31:0] a, b;                            |

| input cin, CLOCK;                             |

| output [31:0] sum;                            |

| output cout;                                  |

| reg [31:0] sum;                               |

| reg cout;                                     |

| reg [32:0] temp;                              |

| always @(a or b or cin)                       |

| begin                                         |

| temp=a+b+cin;                                 |

| end                                           |

|                                               |

| always @(posedge CLOCK)                       |

| begin                                         |

| {cout, sum}<=temp[32:0];                      |

| end                                           |

|                                               |

| endmodule                                     |

|                                               |

Table 3-2 Source code of 32 bit adder.

| Table 3-3 | Test bench of the 32 bit adder. |

|-----------|---------------------------------|

|-----------|---------------------------------|

//file: ~/project/rtl\_verilog/test\_adder.v module test\_adder; reg [31:0] a, b; reg cin, CLOCK; wire [31:0] sum; wire cout; adder32 block1(a, b, cin, CLOCK, sum, cout); //create a clock with a cycle of 100ns initial begin CLOCK = 1'b0;forever #50 CLOCK= ~CLOCK; end initial begin cin=1'b1;a = 32'h0000;b = 32'h0000;\$display("%d a=%h b+%h cin+%h sum+%h cout+%h", \$time, a, b, cin, sum, cout); #100 a = 32'h0000000; b = 32'h0000ffff;\$display("%d a=%h b+%h cin+%h sum+%h cout+%h", \$time, a, b, cin, sum, cout); #100 a = 32'h0000ffff; b = 32'h0000000; \$display("%d a=%h b+%h cin+%h sum+%h cout+%h", \$time, a, b, cin, sum, cout); #100 a = 32'h0000ffff; b = 32'h0000ffff;\$display("%d a=%h b+%h cin+%h sum+%h cout+%h", \$time, a, b, cin, sum, cout); #100 a = 32'h00000000; b = 32'hfff0000;\$display("%d a=%h b+%h cin+%h sum+%h cout+%h", \$time, a, b, cin, sum, cout); #100 a = 32'hffff0000; b = 32'h0000000; \$display("%d a=%h b+%h cin+%h sum+%h cout+%h", \$time, a, b, cin, sum, cout); #100 a = 32'h0000ffff; b = 32'hffffffff; \$display("%d a=%h b+%h cin+%h sum+%h cout+%h", \$time, a, b, cin, sum, cout); #100 a = 32'hfffffff; b = 32'hffffffff; \$display("%d a=%h b+%h cin+%h sum+%h cout+%h", \$time, a, b, cin, sum, cout); #100 a = 32'h00000000; b = 32'h00000000; \$display("%d a=%h b+%h cin+%h sum+%h cout+%h", \$time, a, b, cin, sum, cout); end //finish the simulation at time 1000ns initial begin #10000 \$finish; end

# 3.2.1 Starting NCLaunch

1. Start NCLaunch with the following command in the directory ~/project/rtl\_verilog where the source files are placed.

% nclaunch –new&

where -new specifies that this is a new design. The command *nclaunch* should be used if it is not a new design. At startup, NCLaunch displays a list of modes which users can choose, as shown in figure 3-1.

- Click on Multiple Step.

As this is a new design, user must define a cds.lib and work library. NCLaunch opens the Set Design Directory form as figure 3-6. Do step 3 if the Set Design Directory form doesn't appear, otherwise skip step 3.

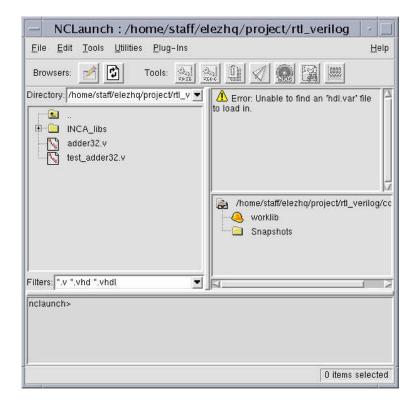

- 3. Choose File→Set Design Directory... from Nclaunch main window as shown in figure 3-5. The Set Design Directory form appears as shown in figure 3-6.

| — NCLaunch : /home/staff/elezhq/project/rtl_verilog                        |              |

|----------------------------------------------------------------------------|--------------|

| <u>Eile Edit Tools U</u> tilities <u>P</u> lug-Ins                         | <u>H</u> elp |

| Browsers: 💉 🛐 Tools: 🔬 🎎 🗐 🗹 🌨 🖼 📖                                         |              |

| Directory: /home/staff/elezhq/project/rtl_v<br>adder32.v<br>test_adder32.v |              |

| Filters: *.v *.vhd *.vhdl                                                  |              |

| nclaunch>                                                                  |              |

| 0 items s                                                                  | elected      |

Figure 3-5 NCLaunch main window.

| _         | Set Design Directory           |

|-----------|--------------------------------|

| -Design D | irectory                       |

| /home/st  | aff/elezhq/project/rtl_verilog |

| Library N | 1apping File                   |

| 1         | Create cds.lib File            |

| -Work Lib | rary                           |

| ОК        | Cancel Help                    |

Figure 3-6 Set Design Directory form.

4. On the Set Design Directory form, click on the **Create cds.lib File** button under the **Library Mapping File** field. This opens the **Create a cds.lib file** form as shown below.

| -         | Ci                                    | reate a cds.li  | b file             |                |

|-----------|---------------------------------------|-----------------|--------------------|----------------|

| Directory | : /home/staff/elezh                   | hq/ASIC/ASIC_da | ta/sim/rtl_verilog | - 1            |

|           |                                       |                 |                    |                |

|           |                                       |                 |                    |                |

| 5         |                                       |                 |                    |                |

| F         | le <u>n</u> ame: <mark>cds.lib</mark> |                 | T.                 | <u>S</u> ave   |

| File      | s of type: Library F                  | Files (*.lib)   | -                  | <u>C</u> ancel |

Figure 3-7 Create a cds.lib file form.

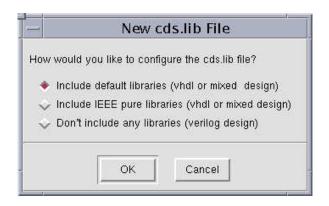

- 5. Click on **Save** to create a library mapping file with the default name cds.lib. NCLaunch opens the **New cds.lib File** form, as shown in figure 3-8. This form lets user pick the libraries that the user wants to use.

- For Verilog files, choose **Don't include any libraries**.

- For VHDL and mixed-language designs, choose either the **default libraries** or **the IEEE pure libraries.**

Figure 3-8 New cds.lib File Form.

6. Click on **OK** to close the New cds.lib File form. NCLaunch displays the main window as shown in figure 3-9.

Figure 3-9 NCLaunch Main Window.

# 3.2.2 Compiling and Elaborating the Design

Before simulating the design, user must

- Compile the source files using the Verilog Compiler<sup>5</sup>, and

- Elaborate the design into a snapshot using the elaborator.

A snapshot is the representation of the design that the simulator uses. The NCLaunch main window gives user access to the tools which user needs when compiling and elaborating design, as well as to several utilities. User accesses the tools and utilities by using the **Tools** or **Utilities** menu or clicking on the appropriate button on the **toolbar**<sup>6</sup>.

The steps of compiling and elaborating are introduced in the following sub-sections.

#### **3.2.2.1** Compiling the Design

- 1. Select the Verilog files that make up the design: adder32.v and test\_adder.v. To select multiple files, hold down the control key and click on each filename.

- 2. Click on the **Verilog Compiler** button. The I/O area at the bottom of the window displays the *ncvlog* command that runs, and it displays the messages that the compiler generates as it compiles the design files.

#### 3.2.2.2 Elaborating the Design

To elaborate a design, user typically expands the work library (**worklib**), select the top-level design unit, and then click on the **Elaborate** button.

<sup>&</sup>lt;sup>5</sup> Use VHDL compiler if the source code is written in VHDL.

<sup>&</sup>lt;sup>6</sup> Refer to section 3.1 for the Tools or Utilities or toolbar.

- 1. Expand the work library (worklib) by clicking on the plus sign next to the hardhat icon.

- 2. Expand the **top-level design unit**. In this example, the top-level is the Verilog testbench, **test\_adder**.

- 3. Select the module.

- 4. Choose **Tools→Elaborator** to open the **Elaborate** form which is shown in figure 3-10.

| - Elaborate           |                           |

|-----------------------|---------------------------|

| Design Unit           | worklib.test_adder:module |

|                       | ([lib.]cell[:view])       |

| 🔟 Snapshot Name       |                           |

| 📕 Work Library        | worklib                   |

| Overwrite log file 🛁  | ncelab.log                |

| Error Limit           | 15 🚽                      |

| 🔟 Update if needed    |                           |

| Access Visibility     | All —                     |

| 🔟 Executable Filename |                           |

|                       | ( Default: ncelab )       |

| ☐ Other Options       |                           |

|                       | Advanced Options          |

| OK Cance              | al Apply Help             |

Figure 3-10 Elaborate Form.

Notice that the **Access Visibility** button is selected and that the value is set to **All**. This option provides full access (read, write, and connectivity access) to simulation objects so that user can probe objects and scopes to a simulation database and debug the design.

- 5. Enable the **Other Options** button and enter **-timescale 1ns/1ns** in the text field.

- Click on Ok to elaborate the design. The I/O area at the bottom of the window displays the *ncelab* command that runs, and it displays the messages that the elaborator generates.

#### **3.2.3** Starting the Simulator

To start the simulator:

- 1. Expand the **Snapshots** folder to display the snapshots that are available in the design library.

- 2. Select the **snapshot**, as shown in figure 3-11.

| <u>File Edit Tools Utilities Plug-Ins</u>    | Help                                                                                                                          |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Browsers: 🧖 🛐 Tools: 🚉                       |                                                                                                                               |

| Directory: elezhq/ASIC/ASIC_data/sim/rtl_v v | /home/staff/elezhq/ASIC/ASIC_data/sim/<br>worklib<br>worklib<br>worklib<br>worklib.<br>snapshots<br>worklib.test_adder:module |

Figure 3-11 Selecting the snapshot.

3. Click on the **Simulator** button.

The **Design Browser** and the **Console** window appear. User can access design hierarchy in the **Design Browser**, and enter '**SimVision** and **simulator**' commands in the **Console** window.

| – Design B                                                                 | rowser 1 – Sim∀ision                                                                                           |                  |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>S</u> elect E <u>x</u> plore Sjn | nulation <u>W</u> indows                                                                                       | <u>H</u> elp     |

|                                                                            | 🚮 🥸 - 🤇 send To: 💽 🧱 🖹 🎇 🖇                                                                                     | V 🖬 🖬            |

| TimeA ▼ = 0 ▼ ns ▼                                                         | ا المعنى الم |                  |

| 🚺 🎹 🔣 i 🐯 🚮 i 🍏 i Simulation T                                             | ime: 0 + 0                                                                                                     |                  |

| Browse: 🧿 All Available Data 🚽 🔍                                           | Signals/Variables of scope:                                                                                    | - 9              |

| Simulator                                                                  | Signal/Variable                                                                                                | Value            |

| Leaf Filter: * 💌                                                           |                                                                                                                | <br>cts selected |

Figure 3-12 Design Browser.

| <ul> <li>Console – SimVision</li> </ul> |             |

|-----------------------------------------|-------------|

| Eile Edit Simulation Windows            | <u>H</u> el |

| j k ta ta ≻.                            |             |

| ▶ 🗰 K   🔁 🔂   Simulation Time: 0 + 0    | 🐼 🗿 📬       |

| ncsim>                                  |             |

|                                         |             |

|                                         |             |

| SimVision simulator                     |             |

Figure 3-13 Console Window.

In the **Design Browser** sidebar on the left side of the window, **SimVision** places the simulation at the top of the hierarchy and assigns it the name **simulator**. The top-level of the design hierarchy is placed below the simulator. In this example, it is named test\_adder.

At startup, the **Console** window has two tabs, as shown in figure 3-13. The **SimVision** tab lets users enter *SimVision* commands and the **simulator** tab lets users enter *simulator* commands. As simulation running, the **Console** window also displays messages from *SimVision* and the *simulator*.

4. After invoking the simulator, user can exit NCLaunch<sup>7</sup>. To exit NCLaunch, bring the NCLaunch main window to the foreground and choose File $\rightarrow$ Exit from the menu bar.

#### **3.2.4** Simulating the Design

**SimVision** lets user choose the simulation data that user wants to save for particular objects or scopes. This can help to keep the size of simulation data files as small as possible. At a later time, user can load a simulation data file back into the Waveform window and re-examine the simulation results.

This section describes how to select simulation data to save and how to run the simulation.

## **3.2.4.1** Selecting the Simulation Data<sup>8</sup> to Save

User can save simulation data by probing the design during simulation and saving the values of the probed objects to a database. There are two types of probe commands:

- Probe<sup>9</sup> a specific object or objects. The values of the specified objects are saved in the database

- Probe a scope or scopes. Users can choose the type of information to save, such as the inputs to that scope, and can choose whether to probe some or all subscopes.

To probe all objects in all scopes, begin at the top module as follows.

- 1. In the **Design Browser**, click on the + *icon* next to top:test\_adder to expand the hierarchy.

- 2. Select the **top** scope. The signal list on the right side of the window displays the signals for the *top* scope, as shown in figure 3-14. The signal list indicates the type of each signal input, output, inout, internal signal, or transaction. User can use the **Leaf Filter** to choose signals which are intended to view.

<sup>&</sup>lt;sup>7</sup> For more information about NCLaunch, user may refer to the NCLaunch User Guide.

<sup>&</sup>lt;sup>8</sup> User can create different simulation database for individual components of design to help debugging, referring to "Managing Simulation Database" in the SimVision User Guide.

<sup>&</sup>lt;sup>9</sup> About enabling, disabling, and deleting probes, or creating new probes, please refer to "Creating and Managing Probes" in SimVision User Guide.

| — Design Browser 1 – SimVision                                                        | + []              |

|---------------------------------------------------------------------------------------|-------------------|

| <u>Eile E</u> dit ⊻iew <u>S</u> elect Explore Simulation <u>W</u> indows              | Help              |

| 🧬   57.   🖙 🗠   🖬 👘 😨 🖬                                                               | : 🕼 🖬 🎯           |

| 🖀 🝢 TimeA 🗹 = 0 🛛 🗹 Isearch Times: Value 🗸                                            | <b>A A</b>        |

| 🗅 🎹 🔣 🙀 🧯 Simulation Time: 0 + 0                                                      |                   |

| Browse: 🧿 All Available Data. 🔄 🔍 Signals/Variables of scope: 🕼 simulator::test_adder |                   |

| 🖂 💏 simulator Signal/Variable                                                         | Value             |

| test_adder                                                                            | 'hxxxxxxxx        |

| 田 <b>物</b> D                                                                          | 'hxxxxxxxx        |

| - 🔤 cin                                                                               | ×                 |

| CLOCK                                                                                 | ×                 |

| cout                                                                                  | ×                 |

| E C sum                                                                               | 'nxxxxxxxx        |

| Leaf Filter: X III Filter: X Filter: X                                                |                   |

| <mark>ම</mark>                                                                        | 1 object selected |

Figure 3-14 Choosing the top scope.

3. **Choose Simulation → Create Probe...** from the **menu bar**.

**SimVision** opens the **Create Probe** form. This form lets user probe one or more levels of *subscope*, choose the type of signals that user wants to probe, and write the probed information to any database.

| - SimVision                   | i: Create Probe 🛛 🕢 📃                                                           |

|-------------------------------|---------------------------------------------------------------------------------|

| Probe Name:                   | (optional)                                                                      |

| × Delete                      | 💠 Add 🛛 🔯 Browser 🝷                                                             |

| Probe these signals and scope | PS: FT                                                                          |

| test_adder                    |                                                                                 |

| '<br>Signal/Scope:            | Add                                                                             |

|                               |                                                                                 |

| Within each scope, include:   |                                                                                 |

| E Scope                       | <ul> <li>☐ Include sub-scopes:</li> <li>☐ Include within each scope:</li> </ul> |

| Store in database: (default)  |                                                                                 |

| ОК                            | Cancel Help                                                                     |

Figure 3-15 Create Probe form.

- 4. For this probe<sup>10</sup>:

- Select **Include sub-scopes** and choose **all** from the drop-down list to include all the sub-scopes in the design.

- Select **Include within each scope** and choose **all** from the drop-down list to include all inputs, outputs, and ports.

- Deselect Add to waveform display.

The form should have the settings shown in figure 3-16.

| — SimVision: Cre                                                                                                      | ate Probe 📃 🖂                                                                            |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Probe Name:                                                                                                           | (optional)                                                                               |

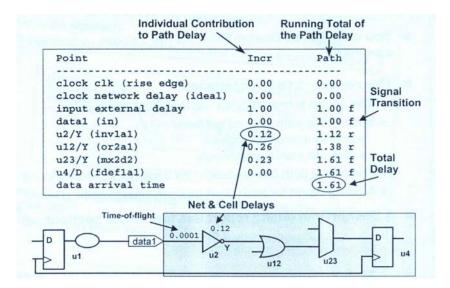

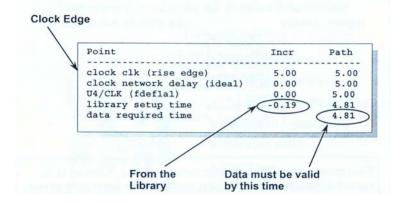

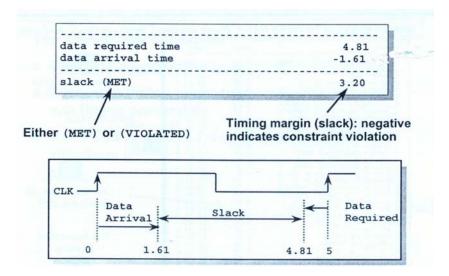

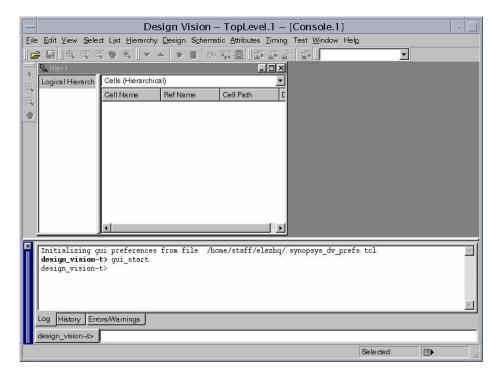

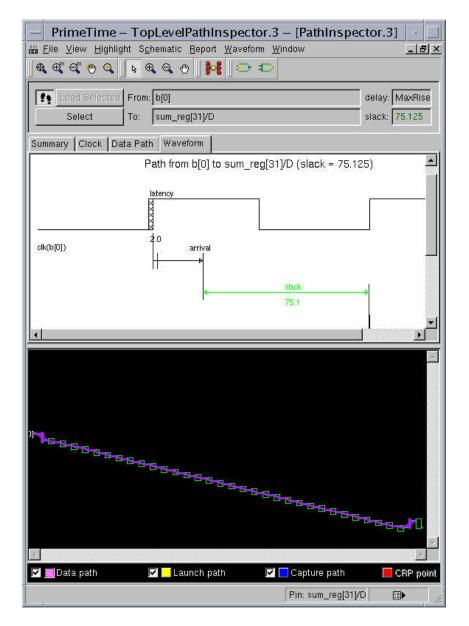

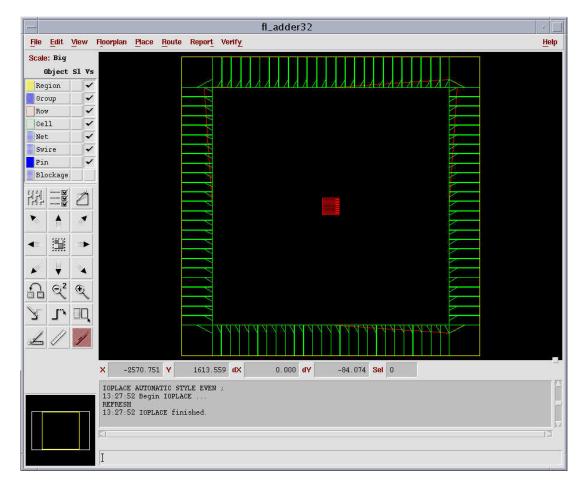

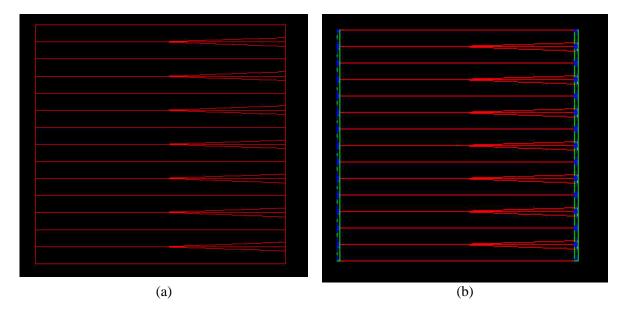

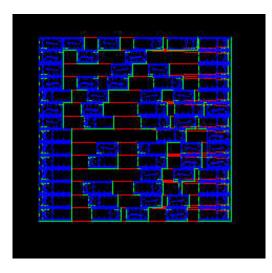

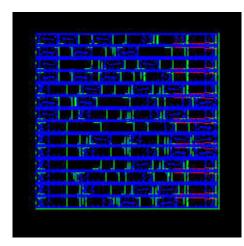

| X Delete Probe these signals and scopes:                                                                              | 💠 Add 🔯 Browser 🔹                                                                        |