# SSMC Dispatching Optimization

IE3100 System Design Project

Team member: BI SIMING, DUONG HAI LONG, TONG YANYAN, WANG FANQI, ZHANG JI, ZHENG YONGMING Supervisor: ASSOC PROF LEE LOO HAY ASST PROF NG SZU HUI

### BACKGROUND

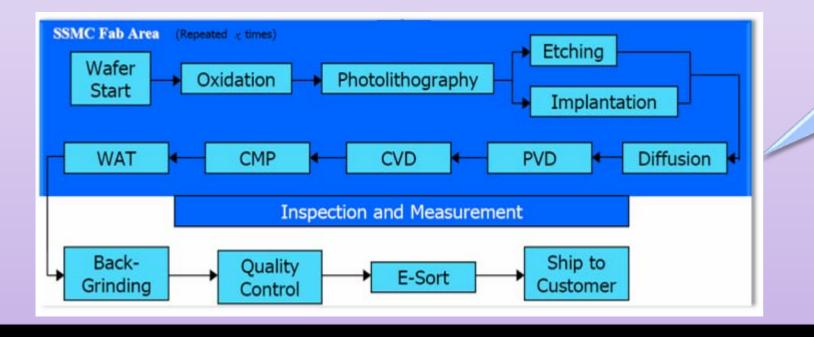

Systems on Silicon Manufacturing Co. Pte. Ltd (SSMC) is a world class semiconductor foundry which supplies chip products to a wide range of industries, by offering flexible and cost effective semiconductor fabrication solutions through the utilization of advanced sub-micron processes.

#### **Basic Definition**

Lot: One processing unit in the fabrication with maximum 25 wafers <u>Furnace and other downstream</u>: Deposition of semi-conductor materials to the wafer surface

## **OBJECTIVES**

#### **PROBLEM DESCRIPTION**

#### Terminologies and Constraints

Stage: set of steps each wafer go through to attain a desired characteristic

Technology: set of characteristics doped to each wafer according to customer's requirement

Recipe: set of instruction carried out by a machine on each wafer

<u>DSP</u>: A number that shows the urgency of a lot, considering all the following criteria

≻Priority type: Super Hot Lot (SHL), Hot Lot, Normal Lot

Critical Ratio: (Time to delivery)/(Remaining processing time)

>OPQT: Maximum queuing time required by certain process steps

Batch Size: The number of wafers in one batch to be loaded into a certain machine

Stage target: The targeted amount of wafer lots to be processed by the end of day for each stage

Develop a *systematic algorithm* for dispatching wafers from wet bench to downstream machines to ≻Satisfy all constraints

≻Meet daily waferout target

Generation of loading priority at Wet Bench

# **APPROACHES AND METHODOLOGY**

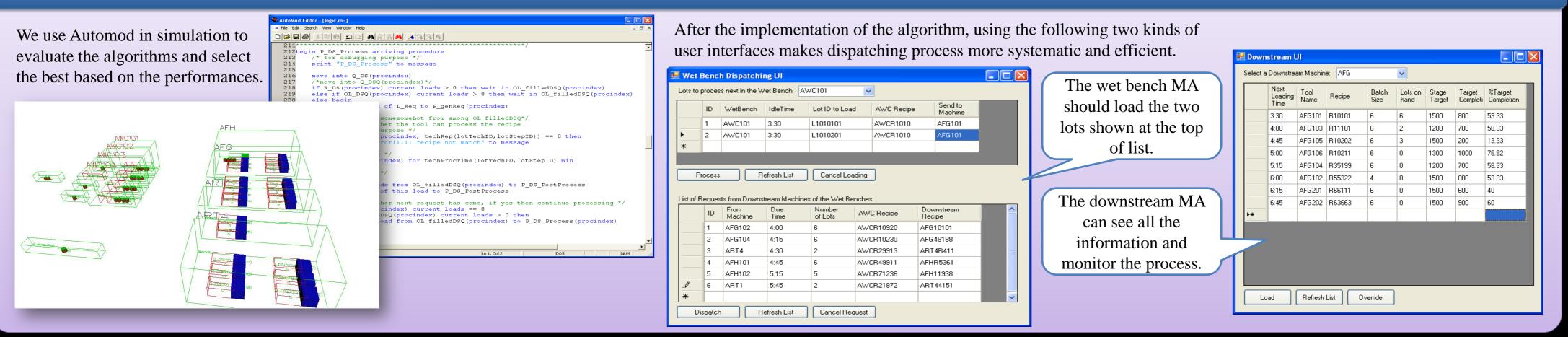

#### Furnace: request generation Wet bench: sort and dispatch the requests Sorting algorithms: Earliest due date, minimum total tardiness, other heuristic rules. Generate next round loading request DSP Framework: whether to use cut off before last round Gather request from down No cut-off Use cut-off streams •Same algorithm all day •By time •Weight of different algorithms depend on •By loading round Switch recipe type Super hot lot time on tools Algorithm Group and sort requests Request Pick by minimum stage target completion Pick by maximum batch size OPQT Last round loading Last round loading Dispatch for the first request Pick by minimum stage target completion from list

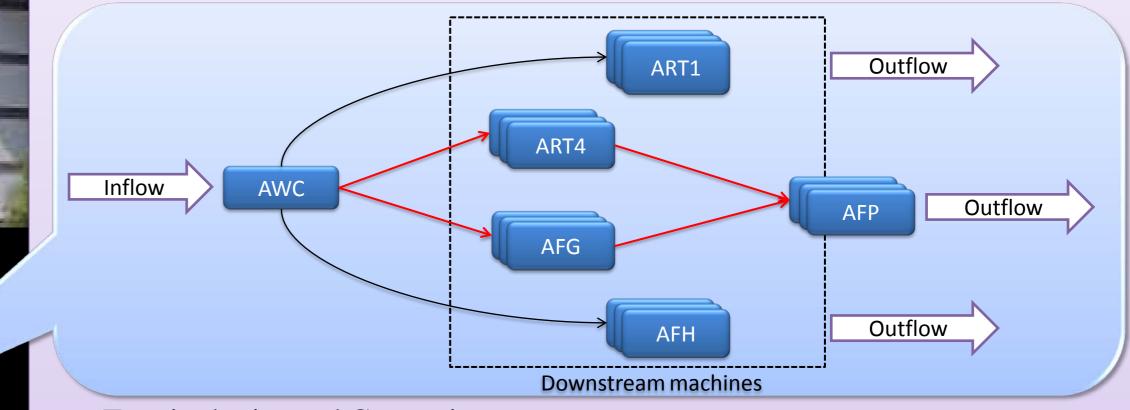

To fully utilize the furnace capacity, a request should be sent to AWC after deciding the wafer recipe to be loaded next round. The request will be generated using the real time information available, such as the lots at AWC and Furnaces. Two basic sorting algorithm can be used: maximum-batch-size (MBS) and minimum-stagetarget-completion (MSTC).

▶<u>MBS algorithm:</u> achieve higher machine efficiency

Problem Description Current dispatching process is established based on global rule to meet delivery: Difficulty to manage tool output based on this global rule Low adaptability to any changes

<u>Recipe type at wet bench:</u> Requests are grouped into long or short recipe request according to required processing time at wet bench.

<u>DSP Priority:</u> Super Hot Lot (SHL) is covered in DSP Priority. Lots with higher priority, by referring to DSP\_Priority must be processed as soon as possible at each step. It jumps the queue in the request list.

➢<u>MSTC algorithm:</u> balance the stage target completion among different stages To achieve the best trade-off of machine utilization and stage target completion, different frameworks are proposed to use MBS algorithm and/or MSTC algorithm.

OPQT: OPQT is the maximum queuing time at downstream tools. Hence, the lots are only processed when there is a request triggered (Controlled by dummy step). Last Round Loading: Last round loading request should not be delayed in order to fulfill the daily stage target.

#### SIMULATION AND IMPLEMENTATION

Department of Industrial and Systems Engineering